## 10.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

### 10.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI<sup>™</sup>)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

An overview of I<sup>2</sup>C operations and additional information on the SSP module can be found in the "*PICmicro*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

Refer to Application Note AN578, "Use of the SSP Module in the  $I^2C^{TM}$  Multi-Master Environment" (DS00578).

### 10.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module.

SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RB2/SDO/RX/DT

- Serial Data In (SDI) RB1/SDI/SDA

- Serial Clock (SCK)

RB4/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS)

RB5/SS/TX/CK

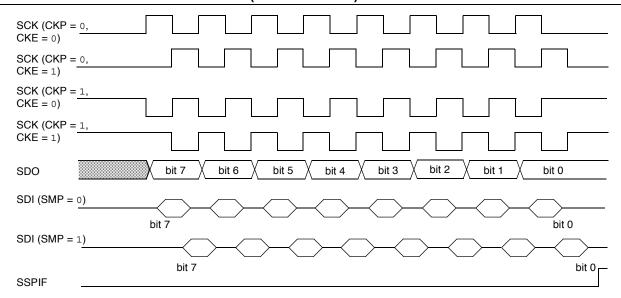

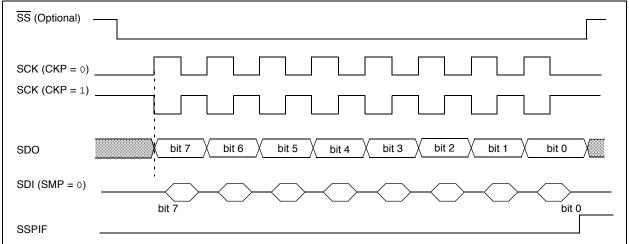

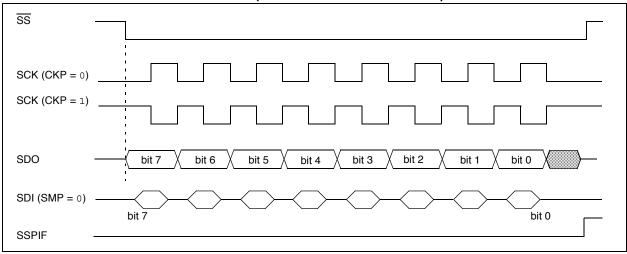

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and the SSPSTAT register (SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

- Note: Before enabling the module in SPI Slave mode, the state of the clock line (SCK) must match the polarity selected for the Idle state. The clock line can be observed by reading the SCK pin. The polarity of the Idle state is determined by the CKP bit (SSPCON<4>).

# PIC16F87/88

|       | R/W-0                                                                                                                                             | R/W-0                                 | R-0                     | R-0          | R-0              | R-0           | R-0          | R-0         |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------|--------------|------------------|---------------|--------------|-------------|--|--|--|

|       | SMP                                                                                                                                               | CKE                                   | D/A                     | P(1)         | S <sup>(1)</sup> | R/W           | UA           | BF          |  |  |  |

|       | bit 7                                                                                                                                             | ORL                                   | DIA                     |              | 0.7              | 10.00         |              | bit 0       |  |  |  |

| bit 7 | SMP: SPL                                                                                                                                          | Data Input Sa                         | ample Phas              | e bit        |                  |               |              |             |  |  |  |

|       | SPI Master                                                                                                                                        | -                                     |                         |              |                  |               |              |             |  |  |  |

|       |                                                                                                                                                   | ata sampled<br>ata sampled            |                         |              |                  | owire)        |              |             |  |  |  |

|       | <u>SPI Slave</u><br>This bit mu                                                                                                                   | <u>mode:</u><br>ist be cleared        | d when SPI              | is used in S | lave mode.       |               |              |             |  |  |  |

|       | <u>I<sup>2</sup>C mode:</u><br>This bit mu                                                                                                        | ist be mainta                         | ined clear.             |              |                  |               |              |             |  |  |  |

| bit 6 | CKE: SPI                                                                                                                                          | Clock Edge S                          | Select bit              |              |                  |               |              |             |  |  |  |

|       | 1 = Transmit occurs on transition from active to Idle clock state<br>0 = Transmit occurs on transition from Idle to active clock state            |                                       |                         |              |                  |               |              |             |  |  |  |

|       | Note:                                                                                                                                             | Polarity of c                         | lock state is           | s set by the | CKP bit (SSI     | PCON<4>).     |              |             |  |  |  |

| bit 5 | D/A: Data/                                                                                                                                        | Address bit (                         | I <sup>2</sup> C mode o | nly)         |                  |               |              |             |  |  |  |

|       | In I <sup>2</sup> C Slave mode:                                                                                                                   |                                       |                         |              |                  |               |              |             |  |  |  |

|       | <ul> <li>1 = Indicates that the last byte received was data</li> <li>0 = Indicates that the last byte received was address</li> </ul>             |                                       |                         |              |                  |               |              |             |  |  |  |

|       |                                                                                                                                                   |                                       | -                       | eived was ad | ddress           |               |              |             |  |  |  |

| bit 4 | •                                                                                                                                                 | <sup>(1)</sup> (I <sup>2</sup> C mode | • /                     |              |                  |               |              |             |  |  |  |

|       | <ul> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> </ul>                              |                                       |                         |              |                  |               |              |             |  |  |  |

| bit 3 | S: Start bit <sup>(1)</sup> (I <sup>2</sup> C mode only)                                                                                          |                                       |                         |              |                  |               |              |             |  |  |  |

|       | <ul> <li>1 = Indicates that a Start bit has been detected last (this bit is '0' on Reset)</li> <li>0 = Start bit was not detected last</li> </ul> |                                       |                         |              |                  |               |              |             |  |  |  |

| bit 2 | <b>R/W</b> : Read/Write Information bit (I <sup>2</sup> C mode only)                                                                              |                                       |                         |              |                  |               |              |             |  |  |  |

|       | Holds the R/W bit information following the last address match and is only valid from address match to the next Start bit, Stop bit or ACK bit.   |                                       |                         |              |                  |               |              |             |  |  |  |

|       | 1 = Read<br>0 = Write                                                                                                                             |                                       |                         |              |                  |               |              |             |  |  |  |

| bit 1 | <b>UA:</b> Update Address bit (10-bit I <sup>2</sup> C mode only)                                                                                 |                                       |                         |              |                  |               |              |             |  |  |  |

|       |                                                                                                                                                   | tes that the u<br>ss does not r       |                         | -            | e address in     | the SSPAD     | D register   |             |  |  |  |

| bit 0 | BF: Buffer                                                                                                                                        | Full Status b                         | it                      |              |                  |               |              |             |  |  |  |

|       | <u>Receive (SPI and I<sup>2</sup>C modes):</u><br>1 = Receive complete, SSPBUF is full<br>0 = Receive not complete, SSPBUF is empty               |                                       |                         |              |                  |               |              |             |  |  |  |

|       |                                                                                                                                                   | n I <sup>2</sup> C mode c             |                         |              |                  |               |              |             |  |  |  |

|       | 1 = Transmit in progress, SSPBUF is full (8 bits)<br>0 = Transmit complete, SSPBUF is empty                                                       |                                       |                         |              |                  |               |              |             |  |  |  |

|       | Note 1:                                                                                                                                           | This bit is cle                       | eared when              | the SSP mo   | dule is disabl   | ed (i.e., the | SSPEN bit is | s cleared). |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| REGISTER 10-2:                                                                                                                                                                                                                                                                                                                                                                                                                           | SSPCON: SYNCHRONOUS SERIAL PORT CONTROL REGISTER (ADDRESS 14h)                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | WCOL SSPOV SSPEN <sup>(1)</sup> CKP SSPM3 SSPM2 SSPM1 SSPM0                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 7 bit 0                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                    | WCOL: Write Collision Detect bit                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ol> <li>An attempt to write the SSPBUF register failed because the SSP module is busy<br/>(must be cleared in software)</li> </ol>                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0 = No collision                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

| bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                    | SSPOV: Receive Overflow Indicator bit                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | In SPI mode:                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>1 = A new byte is received while the SSPBUF register is still holding the previous data. Ir of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. The must read the SSPBUF, even if only transmitting data, to avoid setting overflow. In N mode, the overflow bit is not set since each new reception (and transmission) is in by writing to the SSPBUF register.</li> <li>0 = No overflow</li> </ul> |                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | In I <sup>2</sup> C mode:                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is<br/>a "don't care" in Transmit mode. SSPOV must be cleared in software in either mode.</li> <li>0 = No overflow</li> </ul>                                   |  |  |  |  |  |  |  |  |  |  |

| bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                    | SSPEN: Synchronous Serial Port Enable bit <sup>(1)</sup>                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | In SPI mode:                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>1 = Enables serial port and configures SCK, SDO and SDI as serial port pins</li> <li>0 = Disables serial port and configures these pins as I/O port pins</li> </ul>                                                                                        |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | In I <sup>2</sup> C mode:                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>1 = Enables the serial port and configures the SDA and SCL pins as serial port pins</li> <li>0 = Disables serial port and configures these pins as I/O port pins</li> </ul>                                                                                |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>Note 1:</b> In both modes, when enabled, these pins must be properly configured as input or output.                                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |

| bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                    | CKP: Clock Polarity Select bit                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | <u>In SPI mode:</u><br>1 = Transmit happens on falling edge, receive on rising edge. Idle state for clock is a high level.<br>0 = Transmit happens on rising edge, receive on falling edge. Idle state for clock is a low level.<br>In I <sup>2</sup> C Slave mode: |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | SCK release control                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 = Enable clock                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

| <b>hit</b> 0.0                                                                                                                                                                                                                                                                                                                                                                                                                           | 0 = Holds clock low (clock stretch). (Used to ensure data setup time.)                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |

| bit 3-0                                                                                                                                                                                                                                                                                                                                                                                                                                  | SSPM<3:0>: Synchronous Serial Port Mode Select bits<br>0000 = SPI Master mode, clock = OSC/4                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0000 = SPI Master mode, clock = OSC/4<br>0001 = SPI Master mode, clock = OSC/16                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0010 = SPI Master mode, clock = OSC/64                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0011 = SPI Master mode, clock = TMR2 o <u>utp</u> ut/2<br>0100 = SPI Slave mode, clock = SCK pin. SS pin control enabled.                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0101 = SPI Slave mode, clock = SCK pin. $\overline{SS}$ pin control disabled. $\overline{SS}$ can be used as I/O pin.                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0110 = I <sup>2</sup> C Slave mode, 7-bit address                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0111 = I <sup>2</sup> C Slave mode, 10-bit address<br>1011 = I <sup>2</sup> C Firmware Controlled Master mode (Slave Idle)                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1110 = $I^2C$ Slave mode, 7-bit address with Start and Stop bit interrupts enabled                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1111 = I <sup>2</sup> C Slave mode, 10-bit address with Start and Stop bit interrupts enabled 1000, 1001, 1010, 1100, 1101 = Reserved                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | Larandi                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | -n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown)                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

# PIC16F87/88

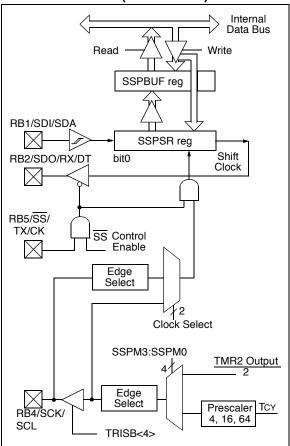

#### FIGURE 10-1: SSP BLOCK DIAGRAM (SPI™ MODE)

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>), must be set. To reset or reconfigure SPI mode, clear bit SSPEN, reinitialize the SSPCON register and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISB register) appropriately programmed. That is:

- SDI must have TRISB<1> set

- · SDO must have TRISB<2> cleared

- SCK (Master mode) must have TRISB<4> cleared

- SCK (Slave mode) must have TRISB<4> set

- SS must have TRISB<5> set

- Note 1: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

- If the SPI is used in Slave mode with CKE = 1, then the SS pin control must be enabled.

| TABLE 10-1: | REGISTERS ASSOCIATED WITH SPI™ OPERATION |

|-------------|------------------------------------------|

|-------------|------------------------------------------|

| Address              | Name    | Bit 7   | Bit 6                                                    | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR |    | all other |      |

|----------------------|---------|---------|----------------------------------------------------------|--------|--------|-------|--------|--------|--------|----------------------|----|-----------|------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE     | PEIE                                                     | TMR0IE | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 00              | 0x | 0000      | 000u |

| 0Ch                  | PIR1    | —       | ADIF <sup>(1)</sup>                                      | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 00              | 00 | -000      | 0000 |

| 8Ch                  | PIE1    | _       | ADIE <sup>(1)</sup>                                      | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 00              | 00 | -000      | 0000 |

| 86h                  | TRISB   | PORTB   | PORTB Data Direction Register                            |        |        |       |        |        |        |                      | 11 | 1111      | 1111 |

| 13h                  | SSPBUF  | Synchro | Synchronous Serial Port Receive Buffer/Transmit Register |        |        |       |        |        |        | XXXX XX              | xx | uuuu      | uuuu |

| 14h                  | SSPCON  | WCOL    | SSPOV                                                    | SSPEN  | CKP    | SSPM3 | SSPM2  | SSPM1  | SSPM0  | 0000 00              | 00 | 0000      | 0000 |

| 94h                  | SSPSTAT | SMP     | CKE                                                      | D/A    | Р      | S     | R/W    | UA     | BF     | 0000 00              | 00 | 0000      | 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI<sup>™</sup> mode. Note 1: This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

## 10.3 SSP I<sup>2</sup>C Mode Operation

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support and provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RB4/ SCK/SCL pin, which is the clock (SCL) and the RB1/ SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISB<4,1> bits. To ensure proper communication of the I<sup>2</sup>C Slave mode, the TRIS bits (TRISx [SDA, SCL]) corresponding to the I<sup>2</sup>C pins must be set to '1'. If any TRIS bits (TRISx<7:0>) of the port containing the I<sup>2</sup>C pins (PORTx [SDA, SCL]) are changed in software during I<sup>2</sup>C communication using a Read-Modify-Write instruction (BSF, BCF), then the I<sup>2</sup>C mode may stop functioning properly and I<sup>2</sup>C communication may suspend. Do not change any of the TRISx bits (TRIS bits of the port containing the I<sup>2</sup>C pins) using the instruction BSF or BCF during I<sup>2</sup>C communication. If it is absolutely necessary to change the TRISx bits during communication, the following method can be used:

#### EXAMPLE 10-1:

**FIGURE 10-5:**

| MOM   |             | Thermals for an 10 min most such as the DIGLEDID (010               |

|-------|-------------|---------------------------------------------------------------------|

| MOVF  | TRISC, W    | ; Example for an 18-pin part such as the PIC16F818/819              |

| IORLW | 0x18        | ; Ensures <4:3> bits are `11'                                       |

| ANDLW | B'11111001' | ; Sets <2:1> as output, but will not alter other bits               |

|       |             | ; User can use their own logic here, such as IORLW, XORLW and ANDLW |

| MOVWF | TRISC       |                                                                     |

|       | 111200      |                                                                     |

The SSP module functions are enabled by setting SSP Enable bit, SSPEN (SSPCON<5>).

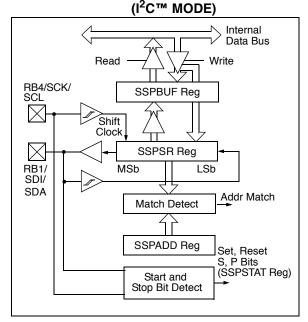

SSP BLOCK DIAGRAM

The SSP module has five registers for I<sup>2</sup>C operation:

- SSP Control register (SSPCON)

- SSP Status register (SSPSTAT)

- · Serial Receive/Transmit Buffer register (SSPBUF)

- SSP Shift register (SSPSR) Not directly accessible

- SSP Address register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled to support Firmware Controlled Master mode

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled to support Firmware Controlled Master mode

- I<sup>2</sup>C Firmware Controlled Master mode operation with Start and Stop bit interrupts enabled; slave is Idle

Selection of any  $I^2C$  mode, with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISB bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the  $I^2C$  module.

Additional information on SSP I<sup>2</sup>C operation may be found in the "*PICmicro*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

#### 10.3.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISB<4,1> set). The SSP module will override the input state with the output data when required (slave-transmitter).

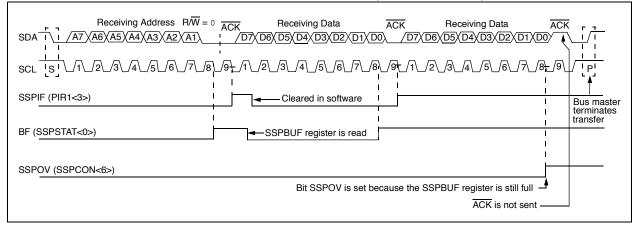

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge (ACK) pulse and then load the SSPBUF register with the received value currently in the SSPSR register.

Either or both of the following conditions will cause the SSP module not to give this ACK pulse:

- a) The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- b) The Overflow bit, SSPOV (SSPCON<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 10-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit, BF, is cleared by reading the SSPBUF register while bit, SSPOV, is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the SSP module, are shown in timing parameter #100 and parameter #101.

#### 10.3.1.1 Addressing

Once the SSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the eight bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The Buffer Full bit, BF, is set.

- c) An  $\overline{ACK}$  pulse is generated.

- d) SSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) – on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave device. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address.

The sequence of events for 10-bit Address mode is as follows, with steps 7-9 for slave transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address; if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

### 10.3.1.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then a no Acknowledge (ACK) pulse is given. An overflow condition is indicated if either bit, BF (SSPSTAT<0>), is set or bit, SSPOV (SSPCON<6>), is set.

An SSP interrupt is generated for each data transfer byte. Flag bit, SSPIF (PIR1<3>), must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

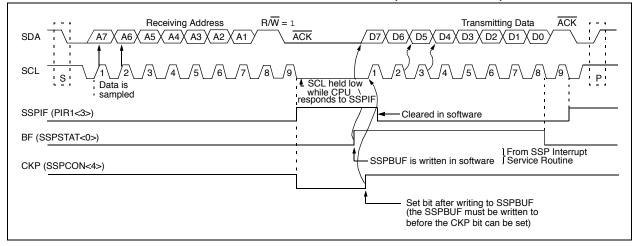

#### 10.3.1.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RB4/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then, pin RB4/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master device must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master device by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 10-7). An SSP interrupt is generated for each data transfer byte. Flag bit, SSPIF, must be cleared in software and the SSPSTAT register is used to determine the status of the byte. Flag bit, SSPIF, is set on the falling edge of the ninth clock pulse.

As a slave transmitter, the  $\overline{ACK}$  pulse from the master receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then

the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave device, the slave logic is reset (resets SSPSTAT register) and the slave device then monitors for another occurrence of the Start bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then, pin RB4/SCK/SCL should be enabled by setting bit CKP.

### TABLE 10-2: DATA TRANSFER RECEIVED BYTE ACTIONS

|          | Status Bits as Data<br>ransfer is Received SSPSR |     | Generate ACK Pulse | Set SSPIF Bit                     |  |  |  |  |

|----------|--------------------------------------------------|-----|--------------------|-----------------------------------|--|--|--|--|

| BF SSPOV |                                                  |     |                    | (SSP Interrupt Occurs if Enabled) |  |  |  |  |

| 0        | 0                                                | Yes | Yes                | Yes                               |  |  |  |  |

| 1        | 0                                                | No  | No                 | Yes                               |  |  |  |  |

| 1        | 1                                                | No  | No                 | Yes                               |  |  |  |  |

| 0        | 1                                                | No  | No                 | Yes                               |  |  |  |  |

Note 1: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

#### FIGURE 10-6: I<sup>2</sup>C<sup>™</sup> WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

#### FIGURE 10-7: I<sup>2</sup>C<sup>™</sup> WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

#### 10.3.2 MASTER MODE OPERATION

Master mode operation is supported in firmware using interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset, or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is Idle and both the S and P bits are clear.

In Master mode operation, the SCL and SDA lines are manipulated in firmware by clearing the corresponding TRISB<4,1> bit(s). The output level is always low, irrespective of the value(s) in PORTB<4,1>. So, when transmitting data, a '1' data bit must have the TRISB<1> bit set (input) and a '0' data bit must have the TRISB<1> bit cleared (output). The same scenario is true for the SCL line with the TRISB<4> bit. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- Start condition

- Stop condition

- · Data transfer byte transmitted/received

Master mode operation can be done with either the Slave mode Idle (SSPM3:SSPM0 = 1011), or with the Slave mode active. When both Master mode operation and Slave modes are used, the software needs to differentiate the source(s) of the interrupt.

For more information on Master mode operation, see Application Note AN554, "Software Implementation of  $l^2C^{TM}$  Bus Master".

#### 10.3.3 MULTI-MASTER MODE OPERATION

In Multi-Master mode operation, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset, or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is Idle and both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In Multi-Master mode operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISB<4,1>). There are two stages where this arbitration can be lost:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave device continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to retransfer the data at a later time.

For more information on Multi-Master mode operation, see Application Note AN578, "Use of the SSP Module in the of  $I^2C^{TM}$  Multi-Master Environment".

| Address                | Name    | Bit 7                                                    | Bit 6               | Bit 5                    | Bit 4    | Bit 3    | Bit 2  | Bit 1  | Bit 0  | Value on POR, BOR |      | Value on<br>all other<br>Resets |      |

|------------------------|---------|----------------------------------------------------------|---------------------|--------------------------|----------|----------|--------|--------|--------|-------------------|------|---------------------------------|------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                                                      | PEIE                | TMR0IE                   | INTOIE   | RBIE     | TMR0IF | INTOIF | RBIF   | 0000              | 000x | 0000                            | 0000 |

| 0Ch                    | PIR1    | _                                                        | ADIF <sup>(1)</sup> | RCIF                     | TXIF     | SSPIF    | CCP1IF | TMR2IF | TMR1IF | -000              | 0000 | -000                            | 0000 |

| 8Ch                    | PIE1    | _                                                        | ADIE <sup>(1)</sup> | RCIE                     | TXIE     | SSPIE    | CCP1IE | TMR2IE | TMR1IE | -000              | 0000 | -000                            | 0000 |

| 13h                    | SSPBUF  | Synchronous Serial Port Receive Buffer/Transmit Register |                     |                          |          |          |        |        |        |                   | xxxx | uuuu                            | uuuu |

| 93h                    | SSPADD  | Synchron                                                 | ous Seria           | Port (I <sup>2</sup> C r | mode) Ad | dress Re | gister |        |        | 0000              | 0000 | 0000                            | 0000 |

| 14h                    | SSPCON  | WCOL                                                     | SSPOV               | SSPEN                    | CKP      | SSPM3    | SSPM2  | SSPM1  | SSPM0  | 0000              | 0000 | 0000                            | 0000 |

| 94h                    | SSPSTAT | SMP <sup>(2)</sup>                                       | CKE <sup>(2)</sup>  | D/A                      | Р        | S        | R/W    | UA     | BF     | 0000              | 0000 | 0000                            | 0000 |

| 86h                    | TRISB   | PORTB D                                                  | ata Direct          | tion Registe             | ər       |          |        |        |        | 1111              | 1111 | 1111                            | 1111 |

TABLE 10-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C<sup>™</sup> OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in SPI™ mode.

Note 1: This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

**2:** Maintain these bits clear in  $I^2C^{TM}$  mode.

# PIC16F87/88

NOTES: